Device Fabrication Mar. 2023 – Dec. 2024

⌜Led the end-to-end cleanroom fabrication of multi-layered silicon quantum dot devices. Utilized a hybrid lithography approach, combining maskless photolithography for large features and E-beam lithography for nanoscale gates. Developed a process for overlaid gate structures requiring high-precision alignment to prevent spurious quantum dots, and implemented manual E-beam focus correction to overcome pattern blurring from large marker topography. The full process involved RIE/wet etching, ALD for dielectric layers, and rigorous AFM/SEM metrology.⌟

In a semiconductor quantum dot device, the precise manipulation of individual electrons is achieved

by applying voltages to metallic nanogates, forming potential landscapes that confine particles and define

the energy levels of a qubit. To meet the exacting nanometer-scale dimensions required, the utilization of

electron-beam (E-beam) lithography becomes imperative for patterning these critical features.

My work involved the complete, end-to-end fabrication of multi-layered silicon quantum dot devices,

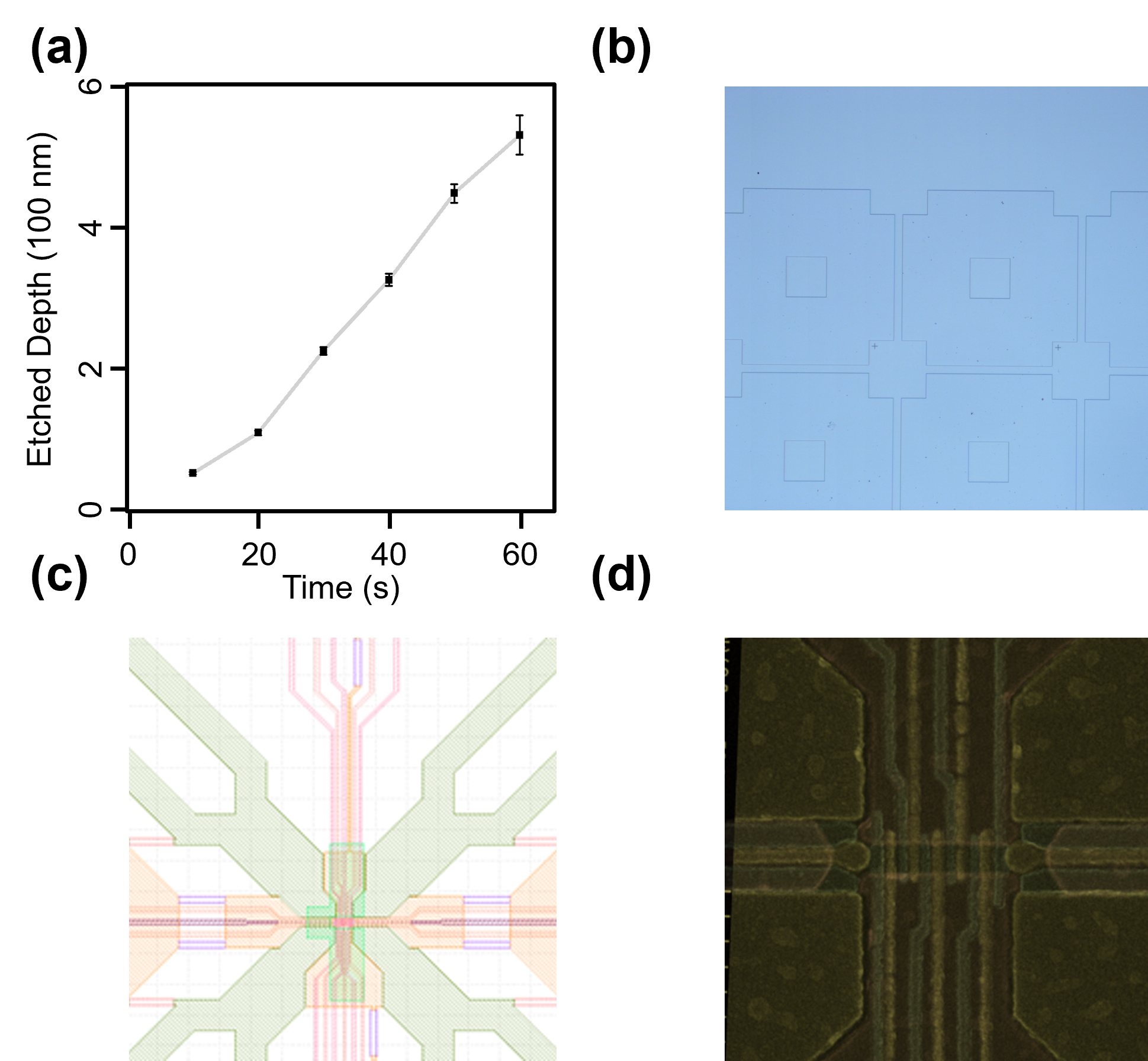

starting from a bare Si/SiGe quantum well wafer. The process began with defining the active device area via

mesa etching, where I gained experience with both dry (Reactive Ion Etching) and wet (chemical)

etching techniques. This was followed by defining ohmic contacts through phosphorus ion implantation and

rapid thermal annealing (RTA).

A critical challenge in silicon is preventing the formation of spurious quantum dots between gates. To address this, we employed an overlaid gate structure, which demands exceptional alignment between multiple layers. To achieve this, I implemented a comprehensive alignment strategy using a full set of P, Q, R, and S markers for maximum precision.

The core of the fabrication relied on a hybrid lithography approach:

I used a maskless photolithography system for large-scale patterns like pads and markers,

and an E-beam lithography system for the fine, nanometer-scale gates.

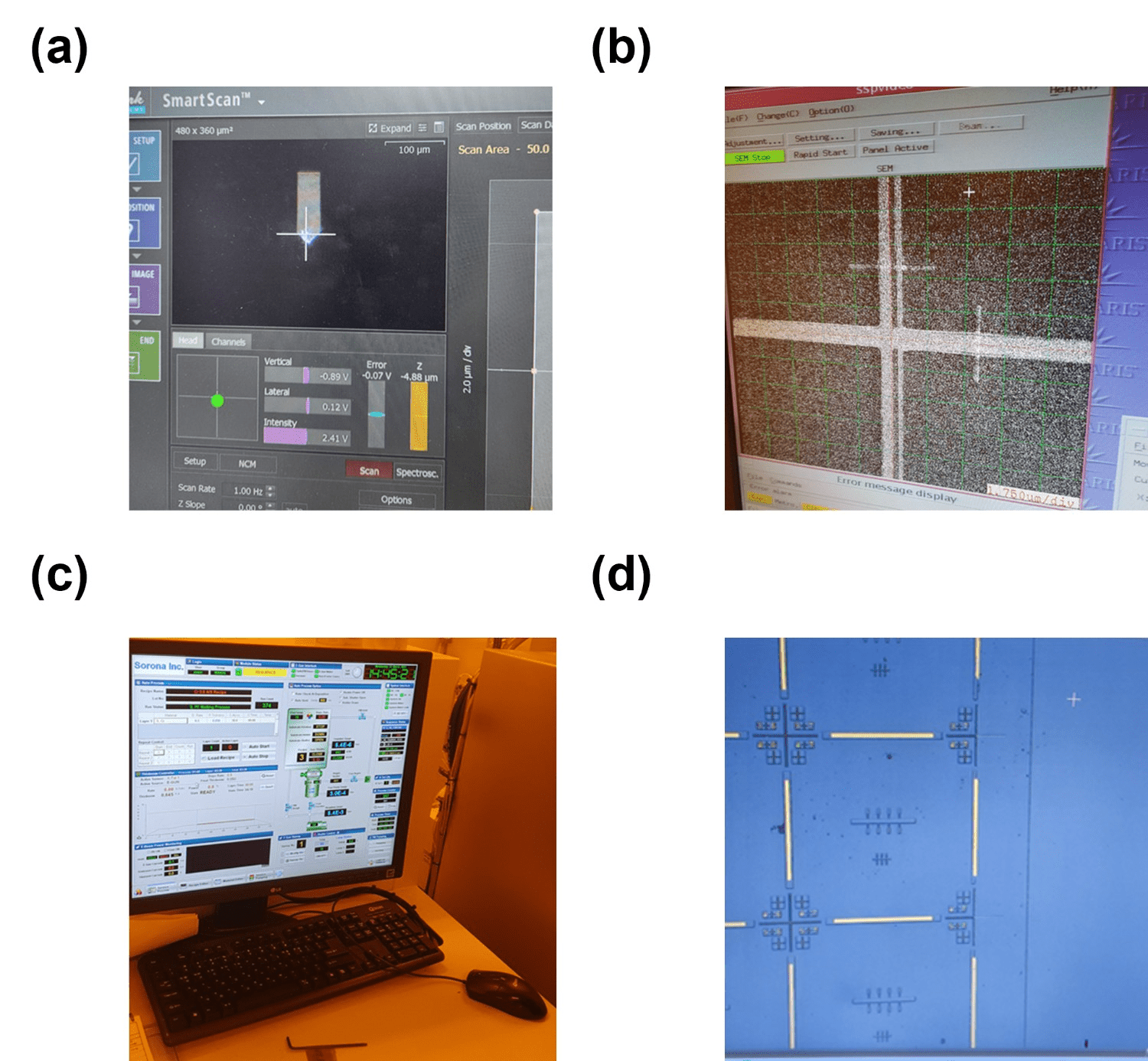

A practical challenge I solved during E-beam writing was the blurring of patterns due to the significant

topography of the pre-etched alignment markers (2-3 µm deep).

To overcome this, I developed a protocol involving manual focus and stigmation adjustments for each marker,

ensuring sharp and accurately placed nanogates.

The multi-layered gate stack was built up through successive steps of E-beam lithography,

metal deposition via E-beam evaporation, and liftoff,

with each gate layer isolated by a thin film of Al₂O₃ deposited via Atomic Layer Deposition (ALD).

Intermediate cleaning steps, such as using O₂ plasma ashing to remove photoresist residue,

were employed to maintain device quality.

Throughout the entire process, rigorous characterization and calibration were performed using tools such as

Atomic Force Microscopes (AFM) and Scanning Electron Microscopes (SEM) to verify critical dimensions,

etch depths, and alignment accuracy. This systematic and detail-oriented approach to fabrication was essential

for producing the high-quality, reliable quantum devices used in my subsequent measurement experiments.